Andrew Huang's Blog, page 28

April 26, 2017

Winner, Name that Ware March 2017

The ware for March 2017 seems to be a Schneider ATV61 industrial variable speed drive controller. As rasz_pl pointed out, I left the sticker unredacted. I had a misgiving about hiding it fearing the ware would be unguessable, but leaving it in made it perhaps a bit too easy. Prize goes to rasz_pl for being the first to guess, email me for your prize!

March 31, 2017

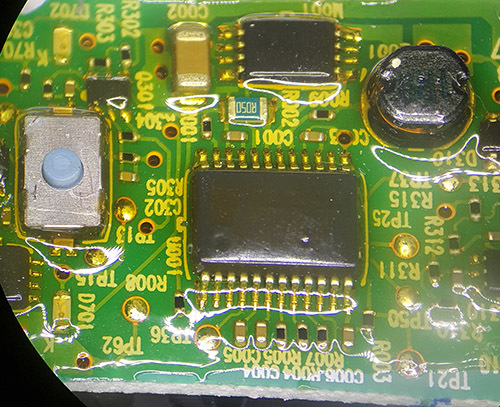

Name that Ware, March 2017

The Ware for March 2017 is shown below.

I honestly have no idea what this one is from or what it’s for — found it in a junk pile in China. But I was amused by the comically huge QFP, so I snapped a shot of it.

Sorry this is a little late — been ridiculously busy prepping for the launch of a line of new products for Chibitronics, going beta (hopefully) next month.

Winner, Name that Ware February 2017

The Ware for February 2017 is a Data Harvest EcoLog.

A number of people guessed it was a datalogger of some type, but didn’t quite identify the manufacturer or model correctly. That being said, I found Josh Myer’s response an interesting read, so I’ll give the prize to him. Congrats, email me for your prize!

March 15, 2017

Looking for Summer Internship in Hardware Hacking?

Tim Ansell (mithro), who has been giving me invaluable advice and support on the NeTV2 project, just had his HDMI (plaintext) video capture project accepted into the Google Summer of Code. This summer, he’s looking for university students who have an interest in learning FPGAs, hacking on video, or designing circuits. To learn more you can check out his post at hdmi2usb.tv.

I’ve learned a lot working with Tim. I also respect his work ethic and he is a steadfast contributor to the open source community. This would be an excellent summer opportunity for any student interested in system-level hardware hacking!

Please note: application deadline is April 3 16:00 UTC.

February 27, 2017

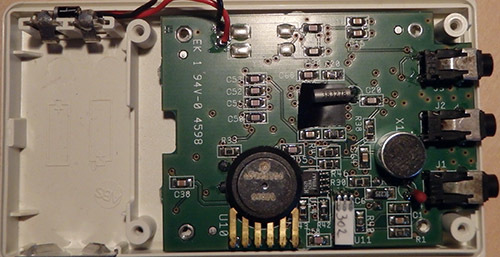

Name that Ware, February 2017

The ware for February 2017 is shown below:

This is a ware contributed by an anonymous reader. Thanks for the contribution, you know who you are!

Winner, Name that Ware January 2017

The Ware for January 2017 is a Philips Norelco shaver, which recently died so I thought I’d take it apart and see what’s inside. It’s pretty similar to the previous generation shaver I was using. Hard to pick a winner — Jimmyjo got the thread on the right track, Adrian got the reference to the prior blog post…from 8 years ago. I think I’ll run with with Jimmyjo as the winner though, since it looks from the time stamps he was the first to push the thread into the general category of electric shaver. Congrats, email me to claim your prize (again)!

January 30, 2017

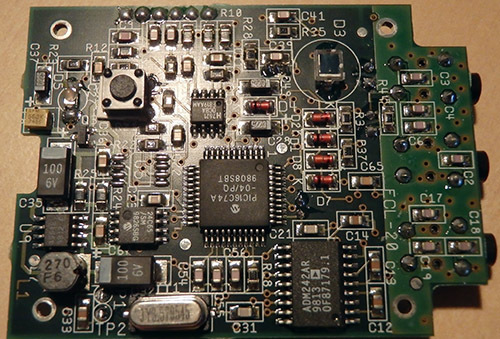

Name that Ware January 2017

The Ware for January 2017 is shown below:

This close-up view shows about a third of the circuit board. If it turns out to be too difficult to guess from the clues shown here, I’ll update this post with a full-board photo; but I have a feeling long-time players of Name that Ware might have too easy a time with this one.

Winner, Name that Ware December 2016

The ware for December 2016 is a diaper making machine. The same machine can be configured for making sanitary napkins or diapers by swapping out the die cut rollers and base material; in fact, the line next to the one pictured was producing sanitary napkins at the time this photo was taken. Congrats to Stuart for the first correct guess, email me for your prize!

December 24, 2016

Name that Ware December 2016

Winner, Name that Ware November 2016

The Ware for November 2016 is a Link Instruments MSO-28 USB scope. Congrats to Antoine for the first guess which got the model number correct, email me for your prize!

Andrew Huang's Blog

- Andrew Huang's profile

- 32 followers